# Proceedings of the

# $9^{th}$ Junior Researcher Workshop on Real-Time Computing

## **JRWRTC 2015**

http://rtns2015.lifl.fr/jrwrtc2015/

Lille, France November 4-6, 2015

#### Message from the Workshop Chair

Welcome to the  $9^{th}$  Junior Researcher Workshop on Real-Time Computing, held in conjunction with the  $23^{rd}$  International Conference on Real-Time and Network Systems (RTNS) in Lille, November 2015. The workshop is a platform for junior researchers to present their work, their incursion into uncharted scientific territories, in a relaxed forum encouraging discussion between members of the real-time community.

I would like to first thank the authors for their submission to the workshop. Each has been reviewed and discussed by the members of the Program Committee, to which I express my gratitude for their dedication to the quality of the selected papers and the workshop. Credit is also due to the General Chair of RTNS Julien Forget (Université de Lille, France), the local committee, Clément Ballabriga, Antoine Bertout and Giuseppe Lipari (Université de Lille, France), and the program chairs, Liliana Cucugrosjean (INRIA Rocquencourt, France) and Nathan Fisher (Wayne State University, USA), for their help and support in organizing the workshop. I also tip my hat to Rob Davis (University of York, UK) and Sebastian Altmeyer (University of Luxembourg, Luxembourg) for their numerous advices in the organisation of the event.

It is with immense delight that, on behalf of the Program Committee, I wish you a pleasant workshop. May the presentations be enjoyable, the posters enlightening, and the discussions fruitful.

Benjamin Lesage (University of York)

#### **Program Committee**

Andreas Abel Saarland University, Germany

Alessandro Biondi Scuola Superiore Sant'Anna, Pisa, Italy

Sudipta Chattopadhyay Linköping University, Sweden

David Griffin University of York, UK

Zhishan Guo University of North Carolina at Chapel Hill, USA

Martijn VAN DEN HEUVEL TU Eindhoven, The Netherlands

Benjamin LESAGE University of York, UK Martina MAGGIO Lund University, Sweden

Ernesto Massa State University of Bahia (UNEB), Brazil

Cristian Maxim Inria Paris, France

Mitra Nasri TU Kaiserslautern, Germany

Borislav Nikolic Polytechnic Institute of Porto, Portugal

### Table of Contents

| Message from the Workshop Chair                                                                                                                | iii |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Failure tolerance for a multicore real-time system scheduled by PD2                                                                            | 1   |

| Discussion on the Spectral Analysis of Real-Time Multi-Path Tasks                                                                              | 5   |

| Scheduling of parallel applications on many-core architectures with caches: bridging the gap between WCET analysis and schedulability analysis | 9   |

| A Comparative Study of the Precision of Stack Cache Occupancy Analyses                                                                         | 13  |

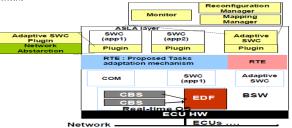

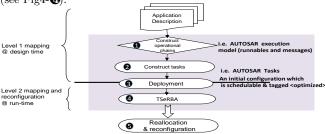

| ASLA: Adaptive System Level in AUTOSAR                                                                                                         | 17  |

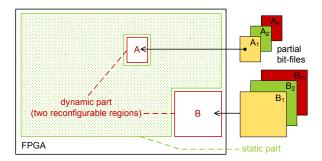

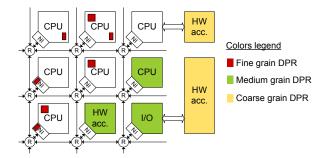

| Towards Utilizing Reconfigurable Shared Resources in Multi-Core Hard Real-Time Systems                                                         | 21  |

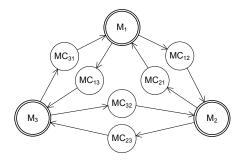

| Regulation versus Flow Control in NoC for Hard Real-time Systems: a Preliminary  Case Study                                                    | 25  |

# Failure tolerance for a multicore real-time system scheduled by PD2

Yves MOUAFO LIAS-ENSMA Teleport 2, 1 av. clément Ader BP 40109,86961 Futuroscope-Chasseneuil yves.mouafo@ensma.fr Annie GENIET

LIAS-ENSMA

Teleport 2, 1 av. clément Ader

BP 40109, 86961

Futuroscope-Chasseneuil

annie.geniet@ensma.fr

Gaëlle LARGETEAU SXlim-SIC, Univ. Poitiers BP 30179, 86962 Futuroscope-Chasseneuil glargeteau@sic.univpoitiers.fr

#### **ABSTRACT**

This work addresses the problem of failure tolerance for real-time applications, running on a multicore hardware architecture. In fact, at any time during the scheduling process, a problem may occur on any of the processor cores, affecting the task that was running on it. We focus on systems composed of periodic independent tasks with simultaneous first release and implicit deadlines. The system is scheduled under the fair algorithm PD2.

Our approach is based on limited hardware redundancy: the system will run on a processor with one more core than required. Then we prove that, if the subtask running on the faulty core is not rescheduled, the application can keep running on the remaining cores without temporal or fairness faults. Moreover, a strategy of restriction and relaxation of tasks deadlines is proposed to ensure the validity and fairness in case of re-execution of the subtask.

#### **General Terms**

Real-time systems, Pfair scheduling, Fault tolerance, limited redundancy, PD2 algorithm

#### **Keywords**

Scheduling, failure, redundancy

#### 1. INTRODUCTION

With the introduction of multicore system-on-a-chip architectures for embedded systems, failure tolerance is bound to become a major aspect in application design. In fact, it is well-known [1] that technology scaling exposes electronic devices to external disturbs. The overall effect is a probability that a core of the processor fails during the execution of the application. In this paper, we focus on permanent failures and adopt the classical modeling of a real-time application [2] which consists of a set of n independent periodic tasks  $\tau = {\tau_1, \tau_2, ..., \tau_n}$ . Each task  $\tau_i$  is submitted to hard temporal constraints and characterized by four temporal parameters: the first release date or offset  $r_i$ , the worst-case execution time (WCET)  $C_i$ , the period  $T_i$  and the relative deadline  $D_i$ . Each task  $\tau$  consists of an infinite set of instances (or jobs). An important characteristic of the task  $\tau_i$  is its utilization  $U_i = \frac{C_i}{T_i}$ . For any system of tasks  $\tau$ , we denote  $U = \sum_{i=1}^{n} (C_i/T_i)$  the load of the system. We assume that the temporal parameters are known and deterministic, the tasks have simultaneous first releases  $(r_i = 0)$  and implicit deadlines  $(D_i = T_i)$ . Thus, we denote a task  $\tau_i$  with a WCET  $C_i$  and a period  $T_i$  by  $\tau_i < C_i, T_i >$ . The system is scheduled under the Pfair algorithm PD2 [3]. Under these assumptions, a necessary and sufficient condition for feasibility is:  $U \le m$  [4] (m denotes the number of processor cores) and PD2 is optimal.

The construction of a PFair scheduling involves dividing each task  $\tau_i$  into unitary subtasks. Each subtask  $\tau_i^j (j \geq 0)$  has a pseudo-release date  $r_i^j = \lfloor \frac{j}{U_i} \rfloor$  and a pseudo-deadline  $d_i^j = \lceil \frac{j+1}{U_i} \rceil$ . The interval  $\lceil r_i^j, d_i^j \rceil$  represents the feasability window of the subtask  $\tau_i^j$ . Subtasks are scheduled in increasing pseudo-deadline order and when the pseudo-deadlines are equal, PD2 uses two additional criterias to determine

the priority order between subtasks.

At any time during the scheduling process, a failure may occur on any of the cores, affecting or not a task. It becomes necessary to reorganize the system so that the system keeps on running on the remaining cores without temporal or fairness failures. To provide a protection against a permanent failure, we propose an approach based on limited hardware redundancy, where only one core is added to those requiered. Thus, we prove that, using a fair algorithm such as PD2, if the affected subtask is not rescheduled, limited redundancy guarantees the validity and the fairness of scheduling despite the defection of one core. Moreover, a strategy of rectriction and relaxation of tasks deadlines is proposed to ensure validity and fairness in case of re-execution of the sutask.

The remainder of this paper is organized in four sections. In the next section (Section 2) a state of the art is introduced. Then our modeling of a failure is proposed, and the limited redundancy approach is presented (section 3). Finally, we present our results to ensure failure tolerance when the re-execution of affected subtask is not necessary (section 4) and when it is (section 5).

#### 2. STATE OF ART

The classical way to provide failure tolerance on multicore platforms (which are generalized by multiprocessors) is to use time and/or space redundancy. Time redundancy can only protect systems against transient faults. However, space redundancy is useful for transient and permanent failures. The idea is to introduce redundant copies of the elements to be protected (processor or other components), and exploit them in the case of a fault. Authors who have dealt with fault tolerance in multiprocessor architectures [5]

[6] prefer to use the primary backup technique where each task has a primary copy and a backup copy. Both copies are scheduled. The backup is only activated when the primary has failed. This technique has drawbacks, due to the increase of the number of processors, induced by the duplication of tasks. Other authors [7] advocates the removal of some tasks after the failure to maintain a tolerable system load. However, this causes a decrease of system functionality. The number of processors used to implement space redundancy is determinant for the energy consumption of the processor and thus has an environnemental impact.

Our approach aims to minimize the number of redundant processors while maintaining the full functionality of the application despite the failure. Therefore, we use only one additional processor and no deletion of task is envisaged. Only the lost subtask might be re-executed. Instead of using the extra core only after the failure (which will be solved by replacing the damaged core by the backup one), we consider that it is used at the begining. This assumption will be necessary in case of re-execution of the lost subtask(s) and thus, we want to study the scheduling behavior in such context.

# 3. FAILURE MODELING AND TOLERANCE APPROACH

#### 3.1 Failure model

We consider that while the application is running, one core of the processor failed. Moreover, the failure is permanent and affects only one subtask: the one that is running on the core which suffers the failure. All or part of this subtask will have to be re-executed. In [8], S. Malo distinguishes two possible scenarios:

- The failure occurs immediately after the context switch. In this case, the application should simply continue execution on the remaining cores. We only have to verify that the reorganization is possible and does not cause a task to miss it deadline;

- The failure occurs during the execution of a task. In this case, three policies are possible: (1) Re-execution of what has been executed since the last backup of the context; (2) The full task is re-executed; (3) The current subtask is simply abandoned and execution continues on the remaining cores.

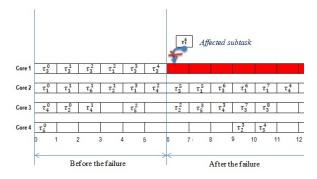

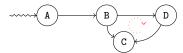

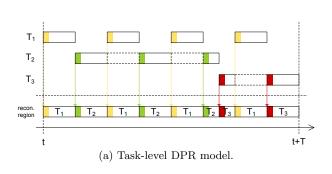

Therefore it is necessary to distinguish the case where the re-execution of task is required (tolerant scheduling with re-execution) and the case where it isn't (tolerant scheduling without re-execution). Figure 1 gives an illustration of the scenarios and draws the outline of the context of our contribution. First, we focus on tolerant scheduling without re-execution which means that no subtask is affected or that possibly affected subtask is abandoned. We must ensure that the application can be keep on running without temporal faults. Then, the case of the re-execution of the affected subtask is discussed in the last section of this paper.

#### 3.2 Limited redundancy approach

Let S be a system of tasks. In the introduction it was established that S is schedulable if and only if  $U \leq m$ . To overcome a failure of a core, limited hardware redundancy is a method which consists in providing an additional core: instead of running S on m cores, it will run on m+1 cores. Thus, when the failure occurs, the system will remain schedulable on the m remaining cores.

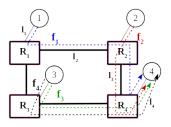

Figure 1: Failure model

Let  $\tau$  be the system of tasks defined by  $\tau=(\tau_1<2,3>,\tau_2<2,6>,\tau_3<3,8>,\tau_4<6,8>,\tau_5<5,12>). The load <math>U=2.54<3$ , thus  $\tau$  is schedulable on a 3 cores processor.

Figure 2 illustrates the use of limited redundancy to build a tolerant scheduling of the system  $\tau$ . A failure occurred on the CPU core 1 at time 6 affecting the subtask  $\tau_1^4$ .

Figure 2: Example of scheduling with limited redundancy method

#### 3.3 Experimentation

A software prototype FTA (Fault Tolerance Analyser) is designed to simulate scheduling with fault by Pfair algorithms. To get concluding results about our approach, a total of 550 random systems with various proportions of heavy task (i.e  $U_i \geq 0.5$ ) has been generated and submitted to the simulation. The fault occurrence time and the failing core of the processor are randomly chosen and vary from one system to another. The experiment was repeated 50 times on the 550 generated systems. The obtained results show that, no matter the time the failure occurs or the affected core, no matter the system load or the number of heavy tasks  $(U_i \geq 0.5)$ , scheduling with fault without reexecution guarantees the respect of validity and fairness constraints.

In the following section, we establish the proof of this result.

#### 4. SCHEDULING WITHOUT REEXECUTION

In this section, we prove that the limited redundancy approach guarantees the validity and the fairness of a tolerant scheduling without re-execution. We introduce the notations and the lemmas needed. The idea of the proof is based

on the observation that tasks are scheduled earlier on m+1 cores with failure than on m core without failure (see lemma

#### 4.1 **Notations and Assumptions**

#### Notations:

$Sched^m$ : PD2-schedule on a m cores architecture, called m-

$Sched^{(m+1)\to m}$ : PD2-schedule on an architecture with m+1functional cores initially, and m cores after a failure, called reorganized-schedule;

$Sched^{m}(t_{i}...t_{j})$ : part of the schedule  $Sched^{m}$  from time  $t_{i}$ to the time  $t_i$ .

$C_m(t)$ :List of pending subtasks at time t in  $Sched^m$ ;

$C^{u}(t)$ :List of subtasks released at time t;

$C_m^e(t)$ :List of the subtasks scheduled at time t in  $Sched^m$ ;  $C_m^r(t)$ :List of the pending subtasks which are not scheduled at time t in  $Sched^m$ ;

$t(\tau_i^j, Sched)$ :Date by which the subtask  $\tau_i^j$  is executed in Sched;

$t_p$ : Failure time;

#### Assumptions:

$U \leq m$  thus  $Sched^m$  and  $Sched^{m+1}$  are valid and fair.

#### Lemmas of interest

Two lemmas are needed to demonstrate our result. For space reason, we state the two lemmas but provide a sketch of proof only for Lemma 2.

Lemma 1: At any time t, the list of the pending subtasks in the reorganized-schedule is included in the list of the pending subtasks in the m-schedule.

$$C_{(m+1)\to m}(t) \subseteq C_m(t)$$

This come from the fact that there are more tasks executed on m+1 cores than on m cores.

Lemma 2:Any subtask is scheduled earlier in the reorganized schedule than in m-schedule.

$$\forall \tau_i^j, t(\tau_i^j, Sched^{(m+1) \to m}) \le t(\tau_i^j, Sched^m)$$

PROOF. Let  $\tau_i^j$  be a subtask. At any time t, if  $\tau_i^j \in C^e_{(m+1) \to m}(t)$  then  $\tau_i^j \in C_{(m+1) \to m}(t)$ .

In fact, if a subtask is scheduled, then it was pending. According the Lemma 1,

$C_{(m+1)\to m}(t)\subseteq C_m(t)$ , therefore,  $\tau_i^j\in C_m(t)$ .

Since at time t a pending subtask is either scheduled or not, we have  $C_m(t) = C_m^e(t) \cup C_m^r(t)$ .

Two cases to consider:

First case:  $\tau_i^j \in C^e_{(m+1)\to m}(t)$  and  $\tau_i^j \in C^e_m(t)$ .

i.e at time t,  $\tau_i^j$  is scheduled in the reorganized schedule and is scheduled in the m-schedule. Then,  $\tau_i^j$  is scheduled at

time t in both schedules:  $t(\tau_i^j, Sched^{(m+1) \to m}) = t(\tau_i^j, Sched^m) = t$

Second case:  $\tau_i^j \in C^e_{(m+1)\to m}(t)$  and  $\tau_i^j \in C^r_m(t)$ .

i.e at time t,  $\tau_i^j$  is scheduled in the reorganized-schedule but is not scheduled in the m-schedule. In this case,  $\tau_i^j$  will be

scheduled later in in the m-schedule. Thus,  $t(\tau_i^j,Sched^{(m+1)\to m})=t$  and  $t(\tau_i^j,Sched^m)>t$ and then  $t(\tau_i^j, Sched^{(m+1)\to m}) \leq t(\tau_i^j, Sched^m)$ .  $\square$

#### 4.3 Validity and fairness proof

Our main result is given by Theorem 1 below.

Theorem 1. Any system  $\tau = (\tau_1 < C_1, T_1 >, \tau_2 <$  $C_2, T_2 >, ..., \tau_n < C_n, T_n >$  which consists of n periodic and independent tasks, with simultaneous first releases and implicit deadlines feasible under the fair algorithm PD2 on a m cores processor and running on m+1 cores, remains feasible on m cores, after the failure of one of the cores without rescheduling the impacted subtask.

In other words, the reorganized schedule  $Sched^{(m+1) \to m}$  is valid and fair. i.e  $\forall \tau_i^j, r_i^j \leq t(\tau_i^j, Sched^{(m+1) \to m}) < d_i^j$ .

PROOF. Let  $\tau_i^j$  be a sub-task. If  $t(\tau_i^j, Sched^{(m+1)\to m}) < t_p$  then  $t(\tau_i^j, Sched^{(m+1)\to m}) = t_p$  $t(\tau_i^j, Sched^{(m+1)})$ , because before the failure, the reorganizedschedule and the (m+1)-schedule are the same.

Since  $Sched^{m+1}$  is valid and fair according to the assumptions, we have

Otherwise  $t(\tau_i^j, Sched^{(m+1) \to m}) < d_i^j$ .  $t_i^j \le t(\tau_i^j, Sched^{(m+1) \to m}) < d_i^j$ .

- The algorithm PD2 can schedule subtasks only if they are pending and so, after their pseudo-release date. Therefore,  $\forall \tau_i^j, r_i^j \leq t(\tau_i^j, Sched^{(m+1) \to m});$

- To prove the second inequality, let us reason by contradiction. Suppose that  $d_i^j \leq t(\tau_i^j, Sched^{(m+1) \to m})$ .

According to Lemma 3,  $t(\tau_i^j, Sched^{(m+1)\to m}) \leq t(\tau_i^j, Sched^m)$ . We would then have  $d_i^j \leq t(\tau_i^j, Sched^m)$ . i.e  $\tau_i^j$  misses its pseudo-deadline and thus,  $Sched^m$  would not be fair. That is contrary to our initial assumptions (see 4.1).

Conclusion:  $\forall \tau_i^j, r_i^j \leq t(\tau_i^j, Sched^{(m+1) \to m}) < d_i^j$

#### SCHEDULING WITH RE-EXECUTION 5.

To take into account the re-execution of the affected subtask, we introduce the "constrain and release" approach; coupled with limited redundancy, it may ensure tolerance. For the implementation, two methods for calculating the tasks deadlines are considered and an experiment is made. We assume, as a first step, that there is a mechanism which detects and locates the affected core [9] during the slot after its occurrence. Therefore only the lost time unit has to be resumed.

#### 5.1 Constrain and release approach

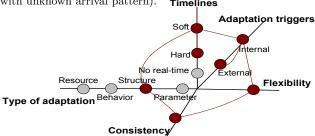

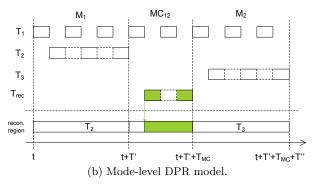

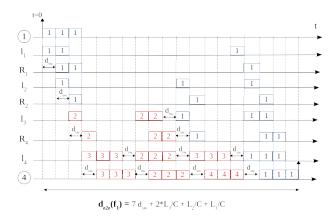

This method consists in starting to scheduling the application on a system of tasks with constrained deadlines, and in releasing the deadlines after failure. Thus the execution begins with smaller feasability windows that will be expanded after the failure. Time margin that is created between deadline and period of a task can be exploited as a tolerance window to possibly re-execute a subtask. Figure 3 illustrates this approach. We build from the starting system (S) (schedulable on m cores), a system with constrained deadlines (S') that runs on m+1 cores. When the failure occurs, the impacted subtask is re-executed in the tolerance window and deadlines are released. We obtain a system S" which continues running on the remaining m cores.

The problem is here to determine how to compute the constrained deadlines, and next how to reconfigure the failed system. In the following paragraphs, we propose some ideas.

Figure 3: Restriction and relaxation approach

#### **5.2** Deadlines calculation

Two approaches are possible. The first consists in exploiting the idle time units of the schedule. Those time units are distributed equally between all instances of all tasks. The proportion of time units allocated to an instance is derived from its period [10].

The second method consists in simulating the addition to each task of a further subtask which represents the re-execution of an affected subtask. The deadline of the task corresponds to the last but one subtask pseudo-deadline.

#### **5.3** Reconfiguration protocol

When a failure occurs at time  $t_p$ , it affects a subtask  $\tau_{i_0}^{'j_0}$  that belongs to the instance  $k_0 = \lfloor \frac{j_0}{C_{i_0}} \rfloor$  of the task  $\tau_{i_0}$ . Constrained deadlines in the system S' must be released for the remainder of the schedule and the failing subtask must be re-executed. Let denote by  $r_i^{'j}$  and  $d_i^{'j}$  respectively the pseudo-release date and the pseudo-deadline of a subtask  $\tau_i^{'j}$  in the running constrained system S'.  $r_i^j$  and  $d_i^j$  are these settings for the corresponding subtask  $\tau_i^j$  in the initial system with implicit deadlines. The reconfiguration happens as follows:

- For the subtasks of non-affected tasks  $\tau'_i(i \neq i_0)$ :

back to initial settings for non-yet executed instances  $(r_i^{'j}, d_i^{'j}) \longmapsto (r_i^j, d_i^j)$ ,  $i \neq i_0$

-For the subtasks of the affected task  $\tau_{i_0}'$ :

keep the settings for the current instance

$$j_0 < j < k_0 C_{i0} \Longrightarrow (r_{i_0}^{'j}, d_{i_0}^{'j}) \longmapsto (r_{i_0}^{'j}, d_{i_0}^{'j});$$

back to initial settings for next instances  $j \ge k_0.C_{i0} \Longrightarrow (r'_{i_0}, d'_{i_0}) \longmapsto (r_{i_0}^j, d_{i_0}^j);$

re-execute the affected subtask  $au_{i_0}^{j_0}$  in the tolerance windows:  $(r_{i_0}^{'j_0}, d_{i_0}^{'j_0}) \longmapsto (D_{i_0}', T_{i_0}).$

#### 5.4 Experimental results

The experimental study, which focused on the same systems than the approach without re-execution (see section 3.3) provided promising results (see Figure 4): whatever the time of the failure, the affected core or the affected task, with the deadlines calculated by the second method, the fairness and the validity of the scheduling seems to be guaranteed. This is also true for most cases with deadlines calculated by the first method. However there are marginal invalid systems that need further extensive study.

|                       |                      | With re-execution            |                                          |

|-----------------------|----------------------|------------------------------|------------------------------------------|

|                       | Without re-execution | Deadlines with<br>1st method | Deadlines with<br>2 <sup>nd</sup> method |

| Validity and fairness | 100%                 | 99%                          | 100%                                     |

Figure 4: Experimental results

#### 6. CONCLUSION AND PERSPECTIVES

In this paper, we proposed the limited hardware redundancy approach to protect a real-time system against a permanent failure of one core. We proved that this approach guarantees validity and fairness of a schedule with failure without re-execution.

When re-execution is necessary, we proposed to constrain the deadlines of tasks before failure and to release them after. This method provided us promising results that we plan to demonstrate in future work. Moreover, we will study the case where re-execution of several subtasks is necessary. We will finally try to determine the maximum tolerable delay between the occurrence of a failure and its detection.

#### 7. REFERENCES

- M. Baleani, A. Ferrari, L. Mangeruca, A. Sangiovanni-Vincentelli, M. Peri, and S. Pezzini, Fault-tolerant platforms for automotive safety-critical applications. In Proceedings of the 2003 international conference on Compilers, Architecture and Synthesis for Embedded Systems, pages 170 to 177, 2003.

- [2] A. Choquet-Geniet, S. Malo, Scheduling an aperiodic flow within a real time system using Fairness properties ARIMA Journal, vol. 18, pp. 93 to 116, 2014.

- [3] J. Anderson, A. Srinivasan, A New Look at Pfair Priorities Rap. tech. TR00 023, University of North Carolina at Chapel Hil, sept. 1999

- [4] S. K. Baruah, N. K. Cohen, C. G. Plaxton, and D. A. Varvel, Proportionate progress: A notion of fairness in resource allocation. *Algorithmica* 15, p.600 to 625,1996

- [5] A. Bertossi, L. Mancini, A. Menapace, Fault-Tolerant Rate-Monotonic first-fit scheduling in hard real-time systems. *IEEE Transactions on parallel and distributed* systems 10,9 (sept 1999) 934-935.

- [6] S. Ghosh, R. Melhem, D. Mosse Fault-tolerance through scheduling of aperiodic tasks in hard real-time multiprocessor systems. *IEEE Transactions on parallel* and distributed systems 8,3 (march 1997) 272-283.

- [7] T. Megel, Placement, ordonnancement et mécanismes de migration de tâches temps-réel pour des architectures distribuées multicoeurs. Thèse de doctorat de l'université de Toulouse, avril 2012.

- [8] S. Malo, Contribution à l'ordonnançabilité des applications temps-réel multiprocesseurs. Thèse de doctorat de l'Ecole Nationale Supérieure de Mécanique et d'Aérotechnique, décembre 2010.

- [9] E. Chanthery, Y. Pencole, Modélisation et intégration du diagnostic actif dans une architecture embarquée Dans Journal Européen des Systèmes Automatisés, MSR 2009, pages 789 to 803, 2009.

- [10] Y. Mouafo, A. Geniet-Choquet, G. Largeteau-Skapin Robustesse des applications temps-réels multicoeurs Actes de l'école d'été temps-réel 2015, pg 143-146.

# Discussion on the Spectral Analysis of Real-Time Multi-Path Tasks

## Fabrice Guet, Luca Santinelli and Jérôme Morio ONERA Toulouse - The French Aerospace Lab, Toulouse

{fabrice.guet|luca.santinelli|jerome.morio}@onera.fr

#### **ABSTRACT**

The Worst-Case Execution Time (WCET) is applied to guarantee the safety critical real-time systems. The increasing complexity of todays real-time systems requires new approaches for evaluating the WCET of a task. Measurement Based Probabilistic Timing Analysis provides safe probabilistic WCET with the Extreme Value Theory (EVT). The theoretical applicability of the EVT relies on assumptions that has to be verified. The spectral analysis of multi-path task proposed in this paper aims at defining the task timing behavior and deducing its worst-case execution path. It gives also measurement guidelines to ensure the EVT applicability in the complex case of multi-path tasks.

#### 1. INTRODUCTION

The safety of real-time system relies on hard timing constraints that have to be respected at every system execution [4]. System predictability is achieved by determining the Worst-Case Execution Time (WCET) of each task that depends on their implementation and the hardware architecture that runs the task. It is the schedulability analysis that guarantees timing constraints by verifying execution requirements of each task by making use of their timing evaluation.

The new functionalities that are offered by multi-core microprocessors e.g., cache memories, pipelines and so on, increase the complexity of the Critical Real-Time Systems. While they enable relevant gains in terms of average performances e.g., energy consumption and timing computation, it becomes hard to guarantee the worst-case performances of such architectures. Determining every state of the system is quite impossible, moreover for the same execution condition the task execution time could be variable due to different interferences happening [12].

Todays systems complexity makes harder to produce WCET estimates through Static Timing Analyses [15], endangering the reliability of static models and impacting estimates confidence [2]. Alternative to deterministic approaches, probabilistic ones tend to emerge from the requirements of the DO-178-B certification levels in aeronautics which corresponds to probabilistic levels. Contrary to deterministic approaches, probabilistic approaches provide probabilistic Worst-Case Execution Time (pWCET) estimates<sup>1</sup>.

In particular, measurement based analysis applies the Extreme Value Theory (EVT) [7] for modeling extreme events such as extreme execution times in order to derive pWCETs. From system performance measurements, in this case execution times, the EVT provides pWCETs with negligible cost by reducing the analysis effort, because it does not require any system model.

Limitation is the proof of the EVT theoretical applicability and so the reliability of the pWCET estimates [10, 14]. As most of statistical models, the EVT requires independent and identically distributed (i.i.d.) measurements to produce pWCETs that is quite difficult to assume in practical problems as those including real-time computing systems.

Current researches focus on the independence problem of the measurements by introducing system randomness e.g., implementing random replacement policies in cache memories. On the one hand, this randomization may be regarded as harmful for real-time system safety [13] and on the other hand, strict independence is not required regarding mathematical conditions to consider the EVT [6].

Considering the timing behavior of a real-time task as a process, EVT conditions are applicable for stationary processes i.e. processes which follow the same probabilistic law. Spectral analysis in signal processing enables to stress the underlying law of the process in presence of noise and could be suitable to ensure the applicability of the EVT. The application of the spectral analysis aims at proving stationarity in the case of tasks with multiple control flow instructions defining multi-path tasks, by identifying the laws composing the task.

#### Contributions.

In this paper we focus on the measurement based probabilistic analyses and especially on the stationarity aspect for guaranteeing the EVT applicability for the WCET problem, especially for multi-path tasks [5]. The analysis particularly stresses software control flows that drive non stationarities in the statistical analysis of real-time tasks. We face non time-randomized systems and multi-path tasks with their challenges for the EVT application.

#### Outline

In section 2, we introduce stationarity analysis concepts with a possible interpretation for real-time computing systems. In section 3, we introduce a framework for the spectral analysis of real-time tasks and a method to compose the spectral analysis of different tasks. In section 4, we make use of the introduced notions in a case study.

#### 2. A STATIONARITY ANALYSIS FOR REAL-TIME COMPUTING SYSTEMS

Execution time measurements  $C_i$  are collected according to end-to-end measurements of a task at discrete instant times  $i \in [1; N]$ , with N the number of execution time measurements. The collection of measurements is a trace  $\mathcal{T}$  of length N defined as the sequence of execution time measurements:  $\mathcal{T} = (C_i)_{i \in [1;N]}$ . From  $\mathcal{T}$ , it exists a finite number of different possible execution times  $C_{(k)}$  and the upper-ordered sequence of

<sup>&</sup>lt;sup>1</sup>pWCETs are alternative to deterministic Worst-Case Execution Times as probabilistic distributions with multiple execution times, each with a probability of happening.

execution times  $\mathcal{T}^{\uparrow}$  is the sequence of the n different execution times such that  $C_{(1)} < \ldots < C_{(n)}$ .

Randomness that occurs in modern multi-core microprocessors recorded in measurements motivates the definition of a random variable for representing the task execution time.

DEFINITION 1 (EXECUTION TIME PROFILE  $\mathcal{C}$ ). Given a trace  $\mathcal{T}$ , the Execution Time Profile (ETP)  $\mathcal{C}$  is the discrete random variable defined on the finite number n of possible execution times  $C_{(k)}$  and we denote  $\Omega = (C_{(k)})_{k \in \llbracket 1;n \rrbracket}$  the set of the different execution times.

The ETP is usually depicted with the Empirical Density Function or histogram of  $\mathcal{T}$  as the discrete function  $p_{\mathcal{C}}$  associating an execution time  $C_{(k)}$  in  $\Omega$  to its probability density  $p_k$ :

$$p_{\mathcal{C}}(C_{(k)}) = p_k \stackrel{def}{=} \frac{1}{N} \sum_{i \le N} \mathbf{1}_{C_i = C_{(k)}}.$$

(1)

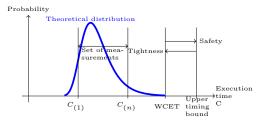

Figure 1: Overview of the WCET problem. Example of a timing probabilistic profile of a task.

While the true task Execution Time Profile should follow a complete theoretical distribution like in Figure 1, the Empirical Density Function is only defined on the set of execution time measurements smaller than the theoretical set of possible execution times due to the difficulty to observe extreme execution times i.e. before  $C_{(1)}$  and after  $C_{(n)}$ .

If there is no obvious reason to assume i.i.d. measurements, one has to consider stationary measurements in order to apply the EVT [6]. In particular, for i.i.d. or stationary weakly dependent measurements whose average probabilistic law has a tail which tends slowly to zero, then the EVT applicability is ensured. Within the scope of non time-randomized hardware architectures, independence is quite hard to assume because of past states in memory units [10] whereas the hypothesis of weakly dependent stationary measurements is more realistic. Hence, we investigate the stationarity in real-time computing systems.

Definition 2 (Strictly Stationary Trace). A trace  $\mathcal{T} = (C_1, C_2, \ldots)$  is a strictly stationary trace if for all j, k, l, the set of execution times  $C_j, \ldots, C_{j+k}$  has the same probabilistic law as the set  $C_{l+j}, \ldots, C_{l+j+k}$ .

Given a trace, if Definition 2 is verified, then there is strong evidence that measurements are identically distributed (i.d.) from the same probabilistic law (e.g., Gaussian, Gumbel, Weibull etc). Since in practice the law is not known there is no chance to prove the i.d. hypothesis so that we consider stationarity instead.

Evidences of non stationarities in real-time computing systems may be

**Deterministic trends:** the execution time evolves according to a function over the time e.g., a *for* loop whose upperbound evolves deterministically over the time.

Random walks: this case may not happen because the current measure cannot be a sum of the preceding one and a random one.

**Seasonalities:** in multi-path programs, one path is executed (one probabilistic law) during an amount of time then another one and so on.

Stationarity is essential in statistical analyses but it is a usually assumed hypothesis in a very wide range of applications. The problem is even more diffcult because there is no practical definition and it sometimes relies on subjective analyses [11]. That is why we consider a statistical metric to evaluate the trace stationarity which are the Kwiatowski Philips Schmidt Shin (KPSS) test [9].

In the real-time computing system domain such non stationarities exposed above could be controlled with measurement rules given by the following spectral analysis.

## 3. A SPECTRAL ANALYSIS OF MULTI-PATH TASKS

In the case of the multi-path task is known, we intend to provide stationarity. Let us consider  $\tau$ , a multi-path task and whose paths are denoted  $\pi_i$  with  $i \in [\![1;\Pi]\!]$ ,  $\Pi$  the number of paths in  $\tau$ . For one executed path  $\pi_i$ , a set of possible execution times  $\overline{\Omega_i}$  cannot be observed. As a consequence, for all possible execution time  $C \in \overline{\Omega_i}$ , the probability to observe C knowing that the path  $\pi_i$  is executed is  $P(C|\pi_i) = 0$ . Thus, execution times in  $\overline{\Omega_i}$  do not follow the same probabilistic law as those in  $\Omega_i$  and so are not identically distributed.

With Definition 2, stationarity would be achieved if measurements are collected for one executed path.  $\forall i \in [\![1;\Pi]\!]$ , the execution time of  $\tau_i$  may be seen as a natural frequency of  $\tau$ . Consequently,  $\tau$ 's timing behavior could be the sum of its natural frequencies, as in signal theory. Consequently, a complete temporal representation of multi-path tasks is required to ensure the investigation of every path for the WCET problem:

DEFINITION 3 (TASK SPECTRAL REPRESENTATION (TSR)). We consider a task  $\tau$  whose paths are denoted  $\tau_i, \forall i \in [\![1;\Pi]\!]$ , where  $\Pi$  is the number of paths.  $\forall i \in [\![1;\Pi]\!]$ , we denote  $\Omega_i$  the set of possible execution times that can take  $\tau_i$ . The Task Spectral Representation of  $\tau$  is a function of the continuous time  $t \in \mathbb{R}^+$ :

$$|\tau|(t) = \frac{1}{\Pi} \sum_{i=1}^{\Pi} \delta_i(t), \tag{2}$$

with  $\delta_i$  the Dirac function that equals to 1 if  $t = T_i$ , where  $T_i$  is a natural frequency of  $\tau$  and 0 otherwise.

The natural frequencies of a task, as defined in signal theory, are either known or deduced from experiments as the execution time that each path takes the most to complete.

For instance, for  $\tau$  running on a fully deterministic single-core microcontroller, if every path of  $\tau$  is executed then  $\forall i \in [\![1;\Pi]\!]$ ,  $\operatorname{card}(\Omega_i) = 1$  and  $\Omega_i = \{T_i\}$ ,  $T_i$  a natural frequency, so the ETP is equal to the TSR of  $\tau$ . In this case, the TSR is a complete timing representation of  $\tau$ . However, for a low deterministic tightly coupled multi-core microprocessor,  $\forall i \in [\![1;\Pi]\!]$ ,  $\operatorname{card}(\Omega_i) > 1$  and so the ETP is different from the spectral representation of  $\tau$ .

The spectral analysis of software tasks is a formalism to have an overview of the timing behavior of the task and manage to collect stationary execution time measurements.

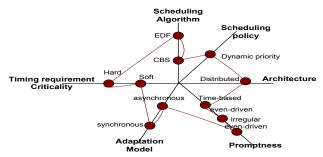

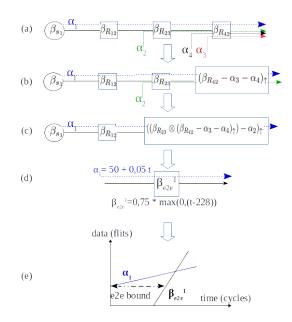

Figure 2: Task  $\tau$ 's graphical representation.

#### TSR Composability.

To ease the worst-case path research, one would like to compose TSRs of known inner tasks included in a task that is the only scheduled. For instance, given a  $(\Pi_1 + 1)$ -path task  $\tau$ , that executes either the known  $\Pi_1$ -path task  $\tau_1$  or a basic block (sequences of instructions that have no control flow instructions) (BB) [3] like in Figure 2, then the TSR  $|\tau|(t) = |\tau_1|(t - \Delta t) + \delta_2(t)$ . The dependent relationship beween  $BB_1$ ,  $\tau_1$  and  $BB_3$  leads to the temporal translation of the TSR  $\tau_1$  of  $\Delta t$  which is the duration of BBs 1 and 3.

Property 1 (TSR Composability). Considering a multipath task  $\tau$  composed of 2 inner tasks  $\Pi_1$ -path task  $\tau_1$  and a  $\Pi_2$ -path task  $\tau_2$  whose TSRs are known then the TSR  $|\tau|$  is

- $|\tau_1| + |\tau_2|$  for independent inner tasks,

- $|\tau_1| \circ |\tau_2| = \frac{1}{\Pi_1 + \Pi_2} \sum_{i=1}^{\Pi_1} \sum_{j=1}^{\Pi_2} \delta_{1_i}(t T_{2_j})$  for dependent inner tasks, where  $T_{2_j}$  is such that  $\delta_{2_j}(T_{2_j}) = 1$ , the natural frequencies of  $\tau_2$ .

Remark 1. • is the convolution operator and is symmetric.

Knowing all TSRs that compose the global task, we deduce analytically the worst-case path by composing all the worst-case paths of every inner tasks. Using the TSR enables to have an overview of the timing behavior of the task to deduce faster the pWCET with the EVT and also guaranteeing stationary measurements for applying the EVT.

Application of the  $\overline{\text{TSR}}$  is presented next for the ns case study from the Mälardelen benchmarks [1].

#### 4. THE NS CASE STUDY

The ns WCET benchmark task searches a key in a 4-dimensional array of 5 elements each. It is a linear search through the array so depending on the key to search there are as many paths as the number of elements in the array. We only consider the farthest element of the last dimension, which makes 4 different paths  $((5-1)\times 5^3)$  each with significant different number of instructions which allows to better visualize the natural frequencies of ns. Thus, the ns TSR is

$$|ns|(t) = \frac{1}{4} \sum_{i=1}^{4} \delta_i(t)$$

(3)

where  $\forall i \in [1; 4], \delta_i$  is also defined by its respective ns input IN which is the key  $KEY_i$  to search. Thus we define,  $\forall i \in [1; 4], IN(\delta_i) = KEY_i$  where  $KEY_i$  is the farthest key in the farthest dimension of the  $i^{th}$  element of the first dimension.

Knowing that every path has the same length it is also possible to define |ns| with the composability (Property 1):

$$|ns|(t) = \frac{1}{4} \left[ \delta_1(t) + \delta_1(t - \Delta t) + \delta_1(t - 2\Delta t) + \delta_1(t - 3\Delta t) \right],$$

(4)

where  $\delta_1$  is the timing function of the first path and  $\Delta t$  the time spent to explore once three dimensions.

#### Hardware Platform.

The platform running the task has two Intel®Xeon®E5620 2.4 GHz sockets, each one with four cores and three levels of cache. The first two levels (L1 and L2) are private to each core, while the last level (LLC, equivalently L3) is shared to the cores belonging to the same socket.

#### Execution Conditions.

The task is running periodically in isolation on one core i.e. there is no other task running on the core and no interrupt (Irq). To guarantee the real-time task execution, we set its scheduling policy to the Linux SCHED\_FIFO policy. The task is executed under different conditions:

- One input: the same input for all instant time.

- Random inputs: the key is randomly modified at each instant time.

- Periodic inputs (100 and 200 iterations case): the key is randomly modified every 100/200 instant times.

Those execution conditions may not be realistic in practice, they stress specific conditions that may be exerced for timing analysis purposes.

#### Results.

We now present the results of the experiments with remarks about stationarity.

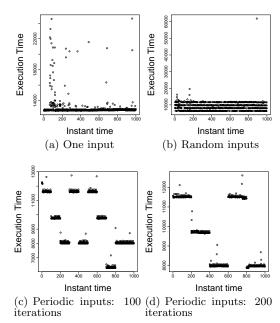

Figure 3: Trace of execution time measurements for every execution condition.

Plots of traces for every execution condition defined above are presented in Figure 3 where execution times are measured in number of cpu cycles. Non determinism is particularly stressed in Figure 3(a) i.e. for one input value, the task execution time takes several different values due to the hardware components. The periodic cases show that the greatest execution time measurement of each path is always lower than the lowest execution time measurement of the following path.

ETPs in Figure 4 support the idea of modeling task execution time with a random variable for non deterministic hardware

Figure 4: Execution Time Profile for every execution condition.

architectures. They highlight the number of different executed paths according to Definition 3: one path in the first case, four paths in the second and third case, and three paths in the fourth case. Filtering the execution times except the peaks of highest probability density (Equation (1)), we deduce the experimental TSR and then the number of probabilistic laws characterizing the timing behavior of the task for the considered architecture.

In addition, we deduce from the ETP in the random case the natural frequencies of ns and the value of  $\Delta t$  in Equation (4), results are in Table 1.

| Path $\delta_i$ | Natural Frequency $T_i$ | $\Delta t$ |

|-----------------|-------------------------|------------|

| 1               | 6300                    | 0          |

| 2               | 8000                    | 1700       |

| 3               | 9750                    | 1750       |

| 4               | 11600                   | 1850       |

Table 1: Determination of the natural frequencies of nsin the random case.

Hypothesis of a constant  $\Delta t$  is confirmed with an error rate of 9%.

With regard to the spectral analysis of ns, stationarity would only be achieved in the first case because only one path is executed.

| Trace $T$ | One path | Random | Period 100 | Period 200 |

|-----------|----------|--------|------------|------------|

| KPSS      | 0.187    | 0.243  | 3.933      | 3.008      |

Table 2: Results of the KPSS test for the different traces of execution time.

Results of the stationarity analysis by the KPSS test, presented in Table 2, highlight the stationarity in the one path case, as we conjectured it in Section 3, and also in the random case. The random case is actually a mixture law that takes into account the four laws composing ns. Blocks of execution time measurements are considered to belong to the same mixture law and explaining why stationarity is achieved. Non stationarities in the last two cases are well detected.

#### 5. CONCLUSIONS

Stationarity is often assumed in stochastic system analyses while it is required to apply statistical models, like the EVT, and derive reliable probabilistic bounds.

While there is no systematic way to prove stationarity, the spectral analysis of real-time multi-path tasks provides a new paradigm to study the stationarity of the timing behavior of a

The spectral analysis also intends to guarantee the task path coverage required to have safe statistical models.

#### References

- WCET project/ Benchmarks, 2013.

S. Altmeyer, B. Lisper, C. Maiza, J. Reineke, and C. Rochange. WCET and mixed-criticality: What does confidence in WCET estimations depend upon? In 15th International Workshop on Worst-Case Execution Time Analysis, WCET 2015, July 7, 2015, Lund, Sweden, pages 65–74, 2015.

- G. Bernat, A. Colin, and S. Petters. pWCET: A tool for probabilistic worst-case execution time analysis of real-time systems. Technical

- G. C. Buttazzo.  $Hard\ Real\mbox{-}Time\ Computing\ Systems:\ Predictable$ Scheduling Algorithms and Applications. The Kluwer international series in engineering and computer science. Kluwer Academic Publishers, Boston, 1997. 3rd edition 2000.

- L. Cucu-Grosjean, L. Santinelli, M. Houston, C. Lo, T. Vardanega, L. Kosmidis, J. Abella, E. Mezzeti, E. Quinones, and F. J. Ca-zorla. Measurement-Based Probabilistic Timing Analysis for Multipath Programs. In the 24th Euromicro Conference on Real-Time Systems, Pise, Italy, July 2012.

- Systems, Fise, Italy, July 2012.

P. Embrechts, C. Klüppelberg, and T. Mikosch. Modelling extremal events for insurance and finance. Applications of mathematics. Springer, Berlin, Heidelberg, New York, 1997.

J. Hansen, S. Hissam, and G. A. Moreno. Statistical-Based WCET

- Estimation and Validation. In 9th International Workshop on Worst-Case Execution Time Analysis (WCET'09), pages 1–11,

- [8] M. Hillary. You can't control what you can't measure, or why it's close to impossible to guarantee real-time software performance on a cpu with on-chip cache. Technical report, Applied Microsystems Corp, 2002.

- D. Kwiatkowski, P. C. B. Phillips, P. Schmidt, and Y. Shin. Testing the null hypothesis of stationarity against the alternative of a unit root: How sure are we that economic time series have a unit root? Journal of Econometrics, 54(1-3):159-178, 00 1992.

- Y. Lu, T. Nolte, I. Bate, and L. Cucu-Grosjean. A Trace-Based Statistical Worst-Case Execution Time Analysis of Component-Based Real-Time Embedded Systems. In 16th IEEE International Conference on Emerging Technology and Factory Automation (ETFA11), WiP session, September 2011

- [11] R. Manuca and R. Savit. Stationarity and nonstationarity in time series analysis. Phys. D, 99(2-3):134–161, Dec. 1996.

- V.-A. Paun, B. Monsuez, and P. Baufreton. On the Determinism of Multi-core Processors. In C. Choppy and J. Sun, editors, 1st French Singaporean Workshop on Formal Methods and Applications (FSFMA 2013), volume 31 of OpenAccess Series in Informatics (OASIcs), pages 32–46, Dagstuhl, Germany, 2013. Schloss Dagstuhl-Leibniz-Zentrum fuer Informatik

- [13] J. Reineke. Randomized caches considered harmful in hard real-time systems. *LITES*, 1(1):03:1–03:13, 2014.

- L. Santinelli, J. Morio, G. Dufour, and D. Jacquemart. On the Sustainability of the Extreme Value Theory for WCET Estimation. In 14th International Workshop on Worst-Case Execution Time

- Analysis, pages 21–30, 2014. R. Wilhelm, J. Engblom, A. Ermedahl, N. Holsti, S. Thesing, D. B. Whalley, G. Bernat, C. Ferdinand, R. Heckmann, T. Mitra, F. Mueller, I. Puaut, P. P. Puschner, J. Staschulat, and P. Stenström. The worst-case execution-time problem - overview of methods and survey of tools. ACM Trans. Embedded Comput. Syst., 7(3),

# Scheduling of parallel applications on many-core architectures with caches: bridging the gap between WCET analysis and schedulability analysis

Viet Anh Nguyen, Damien Hardy, and Isabelle Puaut University of Rennes 1/IRISA, France anh.nguyen@irisa.fr, damien.hardy@irisa.fr, isabelle.puaut@irisa.fr

#### **ABSTRACT**

Estimating the worst-case execution time (WCET) of parallel applications running on many-core architectures is a significant challenge. Some approaches have been proposed, but they assume the mapping of parallel applications on cores already done. Unfortunately, on architectures with caches, task mapping requires a priori known WCETs for tasks, which in turn requires knowing task mapping (i.e., co-located tasks, co-running tasks) to have tight WCET bounds. Therefore, scheduling parallel applications and estimating their WCET introduce a chicken and egg situation. In this paper, we address this issue by developing an optimal integer linear programming formulation for solving the scheduling problem, whose objective is to minimize the WCET of a parallel application. Our proposed static partitioned non-preemptive mapping strategy addresses the effect of local caches to tighten the estimated WCET of the parallel application. We report preliminary results obtained on synthetic parallel applications.

#### 1. INTRODUCTION

Many-core architectures have become mainstream in modern computing systems. Along with them, parallel programming frameworks have been developed to utilize the power of many-core architectures. However, employing many-core architectures in hard real-time system raises many concerns. One significant issue is to precisely estimate the worst-case execution time (WCET) of parallel applications. WCET estimation methods for many-core architecture must take into account not only program paths and architecture (as addressed in WCET estimation methods for uni-core architecture [6]) but also resource contentions (i.e., bus contention and shared memory contention [3]). Moreover, when analyzing the timing behavior of parallel applications, these methods also have to consider the application's properties (i.e., multitasking, inter-task communication and synchronization).

Some approaches reported promising results in estimating the WCET of parallel applications running on many-core architectures. Ozaktas et al. [4] combine the estimated worst-case stall times caused by inter-task synchronization with the tasks' estimated WCETs to compute their worst case response time. Then, the WCET of the parallel application is estimated as the worst case task's response time. In another way, Potop-Butucaru et al. [5] integrate code sections of tasks running on cores as well as communications between them to produce an unified control flow graph. Then, the classical implicit path enumeration technique (IPET [6]) is applied to estimate the WCET of the parallel application.

These two methods assume the mapping of the parallel applications on cores a priori known. However, the mapping of the parallel application influences the worst-case response time of the tasks, and hence affects the WCET of the entire parallel application.

As an illustration, let us consider a parallel application containing three tasks T1, T2, and T3 to be mapped onto on a two-core architecture with a private cache on each core. Let us assume that T1 and T2 access the same memory block m, and that T1 and T2 are independent from T3. Let us consider two mappings: (i) T1 and T2 are assigned to one core and T2 runs after T1, while T3 is assigned to the other core; (ii) T1 is assigned to one core, while T2 and T3 are assigned to the other core and T2 runs after T3. In the first case, T2's access to block m is a hit because m was loaded by T1. Therefore, the WCET of the parallel application in the first case is smaller than in the second case. This small example shows that the WCET of the entire parallel application highly depends on the mapping of its tasks on the cores. This motivates the need for optimal scheduling/mapping of the parallel application to tighten its estimated WCET.

In the literature, many scheduling approaches for parallel applications running on many-core architectures have been proposed [1]. However, most of them consider tasks' WCETs as constant values. As explained above, tasks' WCETs highly depend on the mapping of the applications tasks, due to the effect of private caches. Therefore, scheduling a parallel application without considering the effect of private caches on tasks' WCETs is suboptimal. Consequently, scheduling a parallel application and estimating its WCET are interdependent problems and have to be jointly solved for getting tight estimated WCET of the parallel application.

Ding et al. [2] propose a task scheduling method that minimizes shared cache interferences to tighten estimated WCETs. Their approach is different with us since we consider the effect of private caches in the task scheduling process. Additionally, the communication cost between tasks, which varies depending on task mapping, is not taken into account in [2].

In this paper, we propose a static scheduling solution for an isolated parallel application running on a many-core architecture. Our proposed scheduler not only respects dependence constraints between tasks (i.e., communications and synchronizations) but also takes into account the effect of local caches on tasks' WCETs. We develop an optimal integer linear programming model for solving the task scheduling problem, whose objective is to minimize the WCET of the parallel application. To the best of our knowledge, we are

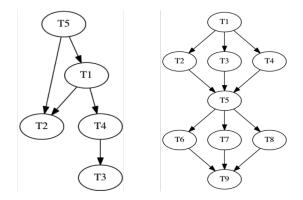

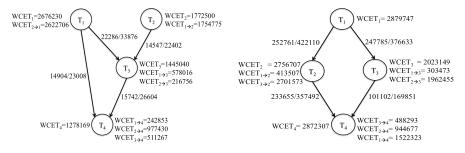

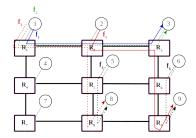

Figure 1: Arbitrary (left) and fork-join (right) task graphs

the first ones considering the effect of private caches on tasks' WCETs when scheduling parallel applications on many-core architectures. Our proposed scheduling approach is a partitioned non-preemptive scheduling approach: tasks are not allowed to be migrated and preempted, which prevents the system from suffering from hard-to predict migration and preemption costs (i.e., mainly caused by losses of working sets stored in local caches).

The paper is organized as follows. Section 2 introduces the application and architecture model, and presents the problem formulation. Section 3 presents an ILP formulation for solving the identified scheduling problem. Section 4 gives preliminary experimental results. Finally, we summarize the content of paper and give directions for future work.

#### 2. MODEL AND PROBLEM FORMULATION

Application model. The parallel application is represented as a directed acyclic task graph (as illustrated in Fig. 1). Following the terminology used in [2], in these graphs, nodes represent tasks (i.e., pieces of code without communication or synchronization inside), and edges represent communications or synchronizations (precedence relations) between pairs of tasks. For each edge, the volume of transmitted data (zero for synchronizations) is known. For example, in the task graph illustrated in Fig. 1, the arrow from node T5 to node T1 means that T1 is not authorized to execute before T5 ends. We consider two instances of the task models: (1) arbitrary model, which does not constrain communications and synchronizations between tasks; (2) the popular fork-join model.

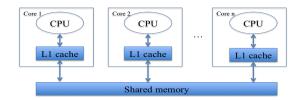

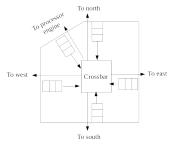

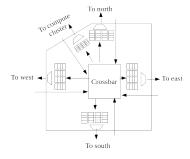

Architecture model. Our proposed scheduler applies to many-core architectures equipped with private caches, including the one depicted in Fig. 2. In the figure, cores are homogeneous and have a private cache. Our model can deal with any type of cache (instruction cache, data cache, and unified cache).

**Problem formulation.** Our scheduling method takes as input the task graph of an isolated parallel application and the following information: (a) the communication costs between tasks (when running on the same core, and when running on different cores); (b) tasks' WCETs when running alone as well as tasks' WCETs when running immediately after another task on the same core (to consider the effect of private caches). As a result the method produces a static partitioned non-preemptive schedule that determines on which cores each task is assigned, as well as a static

Figure 2: An example of many-core architecture with private caches

schedule on each core. The produced schedule minimizes the WCET of the parallel application.

#### 3. ILP FORMULATION OF TASK SCHEDUL-ING/MAPPING PROBLEM

Due to space limitations, only the main ILP constraints are presented hereafter. In the ILP formulation, we use uppercase letters for constants, and lowercase letters for variables to be calculated by the ILP solver. The solution is a set of variables that indicates static task mapping on cores and static task scheduling on each core.

Base constraints for task mapping and scheduling. We define a 0-1 variable  $m_i^k$  to indicate whether task  $t_i$  is assigned to core k or not. Since the proposed scheduler is partitioned, each task is mapped to exactly one core, therefore:

$$\sum_{k \in K} m_i^k = 1. \tag{1}$$

In equation (1), K represents the set of cores. Besides, we define a 0-1 variable  $o_{j\to i}$  to determine whether task  $t_i$  runs right after task  $t_j$  or not, and a 0-1 variable  $f_i^k$  to decide whether task  $t_i$  is the first task running on core k or not. Since the produced schedule is non-preemptive, a task has at most one task running right after it, thus:

$$\sum_{i \in T - \{j\}} o_{j \to i} \le 1. \tag{2}$$

In equation (2), T represents the set of tasks. Additionally, one core has at most one first-running task, therefore, the following constraint is introduced:

$$\sum_{i \in T} f_i^k \le 1. \tag{3}$$

#### Further constraints for task mapping/scheduling.

The objective of the scheduling problem is to minimize the WCET of a parallel application. Let us represent the WCET of the parallel application by an integer variable  $wcet_{pro}$ , the objective function is described as:

minimize

$$wcet_{pro}$$

. (4)

The WCET of the parallel application has to be larger than or equal to the latest finish time of any of its tasks. If the latest finish time of task  $t_i$  is represented by integer variable  $lft_i$ , the following constraint is introduced:

$$wcet_{pro} \ge lft_i, \forall t_i \in T.$$

(5)

In the following, we present the ILP constraints for computing the latest finish time of tasks and for computing the WCET of tasks by considering the effect of local caches.

Constraints on tasks' latest finish times.

The latest finish time of  $t_i$  ( $lft_i$ ) is the sum of its latest start time (denoted as  $lst_i$ ) and its worst case execution time (denoted as  $wcet_i$ ):

$$lft_i = lst_i + wcet_i. (6)$$

In equation (6),  $wcet_i$  is a variable introduced to integrate the variations of tasks' WCETs due to the effect of local caches (as explained later). The latest start time of  $t_i$  ( $lst_i$ ) is the sum of its latest ready time (denoted as  $lrt_i$  which is calculated in considering its running order) as well as the worst communication delay with its predecessors (denoted as  $wc_i$ ):

$$lst_i = lrt_i + wc_i. (7)$$

In equation (7), the worst communication delay of  $t_i$  with its predecessors  $(wc_i)$  is computed by considering the predecessors' allocations, i.e., whether they are allocated on the same core or different cores (as explained later). The latest ready time of  $t_i$   $(lrt_i)$  is calculated by considering two cases: (1)  $t_i$  is the first task running on a core; (2)  $t_i$  runs right after another task on the same core.

In the first case, if  $t_i$  has some predecessor, its latest ready time has to be equal to or larger than the latest finish time of its predecessors since  $t_i$  cannot be executed before the completion of its predecessors. Otherwise, its latest ready time is greater than or equal to zero. Let's denote the set of predecessors of  $t_i$  as  $pred(t_i)$ . The latest ready time of  $t_i$  is expressed as:

$$lrt_i \ge 0$$

$$lrt_i \ge lft_j, \forall t_j \in pred(t_i).$$

(8)

In the second case, if  $t_i$  is assigned to the same core as  $t_j$  and runs immediately after  $t_j$ , then the latest ready time of  $t_i$  is larger than or equal to the latest finish time of  $t_j$ ,  $lrt_i \geq lft_j$ . Therefore, the latest ready time of  $t_i$  in the second case is calculated according to the following constraint:

$$lrt_i \ge o_{j \to i} * lft_j. \tag{9}$$

Since (9) is a quadratic form, we linearize (9) as:

$$lrt_i \ge lft_j + (o_{j \to i} - 1) * M, \tag{10}$$

with M the sum of all tasks' WCETs when running alone plus all communication costs between pairs of tasks when running on different cores, such that M is guaranteed to be higher than the latest finish time of any tasks.

Let us denote the communication cost between  $t_i$  and  $t_j$  when they are placed on the same core and different cores as  $C^s_{j\to i}$  and  $C^d_{j\to i}$ , respectively. The worst communication delay of  $t_i$  ( $wc_i$ ) with its predecessors is calculated as:

$$wc_i \ge s_{i,j} * C_{j \to i}^s + (1 - s_{i,j}) * C_{j \to i}^d, \forall j \in pred(t_i).$$

(11)

In equation (11),  $s_{i,j}$  is a 0-1 variable to indicate whether two tasks  $t_i$  and  $t_j$  are assigned to the same core or not.

#### Constraints on tasks' WCETs.

To account for the variability of tasks' WCETs due to private caches, two cases have to be considered when calculating the WCET of a task  $t_i$  (variable  $wcet_i$ ): (1)  $t_i$  is the first task running on a core; (2)  $t_i$  runs right after another task. Let's denote by  $WCET_i$  the WCET of  $t_i$  when running alone, and  $WCET_{j\rightarrow i}$  as the WCET of  $t_i$  when running right after  $t_j$  on the same core. In the first case, the WCET of  $t_i$  is equal to its WCET when running alone,  $wcet_i = WCET_i$ . In the second case, the WCET of  $t_i$  is equal to its WCET

when running right after another task,  $wcet_i = WCET_{j\rightarrow i}$ . The WCET of  $t_i$  is calculated as:

$$wcet_i = \sum_{j \in T - \{i\}} o_{j \to i} * WCET_{j \to i} + \sum_{k \in K} f_i^k * WCET_i.$$

(12)

#### 4. EXPERIMENTAL RESULTS

Our scheduling approach was evaluated on synthetic task graphs of isolated parallel applications. The communication cost between two tasks  $t_i$  and  $t_j$  when running on the same core  $(C^s_{j\to i})$  and different cores  $(C^d_{j\to i})$  is generated randomly with the constraint  $C^s_{j\to i} < C^d_{j\to i}$ . The WCET of task  $t_i$  when running right after task  $t_j$  is calculated according to the following equation:

$$WCET_{j\to i} = WCET_i - r_{i,j} * WCET_i.$$

(13)

In equation (13), in order to address the effect of local caches on tasks' WCETs,  $r_{i,j}$  ( $0 \le r_{i,j} < 1$ ) is randomly chosen according to the relation between  $t_i$  and  $t_j$ ; the range of  $r_{i,j}$  in case  $t_j$  is direct predecessor of  $t_i$  is higher than that in case  $t_j$  is indirect predecessor of  $t_i$  and that in case  $t_j$  and  $t_i$  are independent.

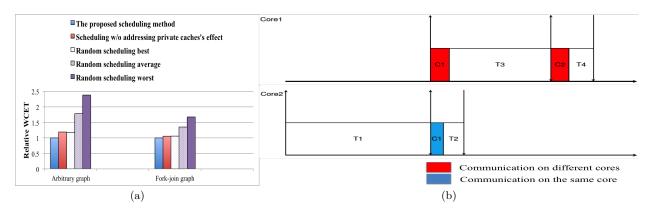

In order to evaluate the performance of the proposed scheduler, we compare the WCET values obtained by our proposed scheduling method (S\_CACHE), a random scheduling method (S\_RAND) and scheduling method without taking into account the effect of private caches (S\_NOCACHE). The smaller the WCET, the better the scheduling method. For S\_RAND, we first randomly allocate tasks to cores, then tasks scheduling on each core is calculated such that communication/synchronization constraints are respected. We generate 10 schedules using S\_RAND and report the best, average and the worst of the estimated WCETs. For S\_NOCACHE, we apply the proposed ILP formulas for getting the schedule, but the WCET of a task when running right after another task on the same core is considered to be equal to its WCET when running alone  $(WCET_{j\rightarrow i} = WCET_i)$ ; when estimating the WCET of the entire parallel application, tasks' WCETs are re-evaluated by considering the effect of private caches. We use CPLEX version 12.5 as ILP solver.

For space considerations, we provide results for two examples of task graphs only (see Fig. 3). In the example of fork-join graph (illustrated in Fig.3), the communication cost between two tasks  $t_1$  and  $t_3$  when running on the same core is 247785 cycles, and when running on different cores is 376633 cycles. In our example, the range of  $r_{i,j}$  in case  $t_j$  is direct predecessor of  $t_i$  is set to [0.6;0.9], the range of  $r_{i,j}$  in case  $t_j$  is indirect predecessor of  $t_i$  is set to [0.2;0.5], and the range of  $r_{i,j}$  in case  $t_i$  and  $t_j$  are independent is set to [0;0.1].

Fig. 4(b) gives the static schedule obtained by our method for our example of fork-join graph on a two-core architecture equipped with a private cache per core. In the schedule, up arrows denote ready time of tasks  $(lrt_i)$ , while down arrows denote the finish time of tasks  $(lft_i)$ . Colored boxes represent communications (in this specific case, there is no overlap between communications and computations, but overlaps may happen in the general case).

Fig. 4(a) compares estimated WCETs obtained when using the different scheduling methods for our example of arbitrary graph and fork-join graph. We normalize all results with respect to the WCET value obtained by S\_CACHE. Our scheduling method generates schedules that lead to the smallest estimated WCET. Moreover, the WCET obtained

Figure 3: Our example of arbitrary graph and fork-join graph.

Figure 4: (a) WCET comparison between different scheduling methods and (b) scheduling graph of tested fork-join graph.

by S\_CACHE is less than 43% in our example of arbitrary graph and 26% in our example of fork-join graph when compared with the average results of S\_RAND. The sizes of the test graphs is small, leading to a small solution space, explaining why S\_RAND finds a schedule as good as S\_CACHE (i.e., in our example of fork-join graph, the best WCET obtained by S\_RAND is more than 5% when compared to the WCET obtained by S\_CACHE). Additionally, compared to S\_NOCACHE, we achieve 16% reduction in WCET in our example of arbitrary graph and 5% reduction in WCET in our example of fork-join graph, which shows the interest of considering the effect of private caches on tasks' WCETs in task scheduling. Furthermore, the runtime of our scheduling approach for these two graphs is very small (10 milliseconds on a 3GHz Intel Core i7 CPU with 16GB of RAM).

#### CONCLUSION 5.

In this paper, we have developed an ILP formulation for finding an optimal schedule for a parallel application on a many-core architecture. Experimental results show the advantage of the proposed scheduler when considering the effect of private caches on tasks's WCETs. In the future, we will investigate the scalability of the proposed scheduling strategy by applying it to synthetic graphs with larger size, as well as to real applications. Additionally, we will address the effect of shared resource interferences (i.e., shared bus) in task scheduling.

#### ACKNOWLEDGMENTS

This work was supported by PIA project CAPACITES (Calcul Parallèlle pour Applications Critiques en Temps et Sûreté), reference P3425-146781). The authors would like to thank Benjamin Rouxel for comments on earlier versions of this paper.

- **7.** REFERENCES[1] R. I. Davis and A. Burns. A survey of hard real-time scheduling for multiprocessor systems. ACM computing surveys, 2011.

- [2] H. Ding, Y. Liang, and T. Mitra. Shared cache aware task mapping for wert minimization. Asia and south pacific Design automation conference (ASP-DAC), 2013.

- G. Fernandez, J. Abella, E. Quiñones, C. Rochange, T. Vardanega, and F. J. Cazorla. Contention in multicore hardware shared resources: Understanding of the state of the art. International workshop on worst-case execution time analysis (WCET), 2014.

- [4] H. Ozaktas, C. Rochange, and P. Sainrat. Minimizing the cost of synchronisations in the weet of real-time parallel programs. International workshop on software and compiler for embedded systems (SCOPES), 2014.

- [5] D. Potop-Butucaru and I. Puaut. Integrated worst-case execution time estimation of multicore applications. International workshop on worst-case execution time analysis (WCET), 2013.

- R. Whilhelm, J. Engblom, A. Ermedahl, N. Holsti, S. Thesing, D. Whalley, G. Bernat, C. Ferdinand, R. Heckmann, T. Mitra, F. Mueller, I. Puaut, P. Puschner, J. Staschulat, and P. Stenström. The worst-case execution time problem: overview of methods and surveys of tools. ACM transactions on embedded computing systems, 2008.

# A Comparative Study of the Precision of Stack Cache Occupancy Analyses

Amine Naji U2IS ENSTA ParisTech Université Paris-Saclay amine.naji@ensta-paristech.fr Florian Brandner

LTCI, CNRS

Telecom ParisTech

Université Paris-Saclay

florian.brandner@telecom-paristech.fr

#### **ABSTRACT**

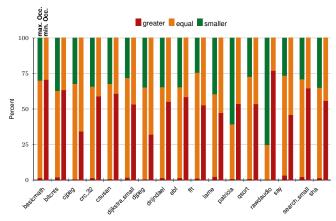

Utilizing a stack cache in a real-time system can aid predictability by avoiding interference between accesses to regular data and stack data. While loads and stores are guaranteed cache hits, explicit operations are required to manage the stack cache. The (timing) behavior of these operations depends on the cache occupancy, which has to be bounded during timing analysis. The precision of the computed occupancy bounds naturally impacts the precision of the timing analysis. In this work, we compare the precision of stack cache occupancy bounds computed by two different approaches: (1) classical inter-procedural data-flow analysis and (2) a specialized stack cache analysis (SCA). Our evaluation, using MiBench benchmarks, shows that the SCA technique usually provides more precise occupancy bounds.

#### **Categories and Subject Descriptors**

F.3.2 [Logics and Meanings of Programs]: Semantics of Programming Languages—Program analysis; C.3 [Special-Purpose and Application-Based Systems]: Real-time and embedded systems

#### Keywords

Program Analysis, Stack Cache, Real-Time Systems

#### 1. INTRODUCTION

To meet the timing constraints in systems with hard deadlines, the worst-case execution time (WCET) of software needs to be bounded. Many features of modern processor architectures, such as caches, improve the average performance, but have an adverse effect on WCET analysis. Time-predictable computer architectures [7] thus propose alternative designs that are easier to analyze, particularly focusing on the memory hierarchy [5, 6]. One such design is the stack cache [1, 8], i.e., a cache for stack data complementing a regular data cache. This promises improved analysis precision, since unknown access addresses can no longer interfere with stack accesses (and vice versa). Secondly, the stack cache design is simple and thus easy to analyze [4].

The cache can be implemented using a circular buffer using two pointers: the memory top pointer MT and the stack top pointer ST. The ST points to the top element of the stack and data between ST and MT is present only in the cache. The remaining data above MT is available only in main memory. In contrast to traditional caches, memory accesses are guaranteed hits and the compiler (programmer) is responsible to enforce that all stack data is present in the cache when needed using three stack control instructions: reserve (sres), free (sfree), and ensure (sens). The worst-case (timing) behavior of these instructions only depends on the worst-case spilling and filling of sres and sens respectively, which can be bounded by computing the maximum and minimum cache occupancy [4], i.e., the value of MT – ST.

Stack cache occupancy bounds, and the associated spill/fill costs can be computed using the recently proposed Stack Cache Analysis (SCA) [4]. The approach splits the analysis problem into several smaller steps, using context-insensitive data-flow analyses to capture function-local properties and longest/shortest path searches on the call graph to model calling contexts. An alternative solution would be to simply model the problem as a traditional inter-procedural dataflow analysis (iDFA) [2]. This appears simpler to implement, as the various steps of SCA are modeled in a single concise analysis. However, the impact on analysis precision has not been investigated so far. Indeed, overestimating the occupancy can increase the spill costs associated with sres instructions, while underestimating the occupancy can increase the fill costs of sens instructions. This work thus compares the precision of the two analysis approaches with respect to the attained max./min. occupancy bounds.

The paper is structured as follows: Section 2 provides some background related to the stack cache as well as static program analysis. We then present the two approaches to analyze the occupancy bounds for the stack cache. The analyses are evaluated in Section 4 before concluding.

#### 2. BACKGROUND

The stack cache is implemented as a ring buffer with two pointers [1]:  $stack\ top\ (ST)$  and  $memory\ top\ (MT)$ . The top of the stack is represented by ST, which points to the address of all stack data either stored in the cache or in main memory. MT points to the top element that is stored only in main memory. The stack grows towards lower addresses.

The difference MT-ST (occupancy) represents the amount of occupied space in the stack cache, which cannot exceed the size of the cache's memory |SC|, thus  $0 \leq \text{MT-ST} \leq |SC|$ .

<sup>&</sup>lt;sup>1</sup>We assume that the stack grows towards lower addresses.

The stack control instructions manipulate the two stack pointers and initiate memory transfers to/from the cache to main memory, while preserving the equation from above. A brief summary is given below, details are available in [1]:

sfree k: Add  $k \leq |SC|$  to ST. If this would result in MT < ST, MT is set to ST. Memory is not accessed.

sens k: Ensure that the occupancy is larger than  $k \leq |SC|$ . If this is not the case, a memory fill is initiated to increment MT until MT - ST  $\geq k$ .

The compiler manages the stack frames of functions quite similar to other architectures with exception of the ensure instructions. For brevity, we assume a simplified placement of these instructions. Stack frames are allocated upon entering a function (sres) and freed immediately before returning (sfree). A function's stack frame might be (partially) evicted from the cache during calls. Ensure instructions (sens) are thus placed immediately after each call. We also restrict functions to only access their own stack frames.<sup>2</sup>

#### 2.1 Data-Flow Analysis

Data-flow analysis (DFA) is used to gather information about a program without executing it. A DFA is a tuple  $A = (\mathcal{D}, T, \sqcap)$ , where  $\mathcal{D}$  is an abstract domain (e.g., values of stack pointers), transfer functions  $T_i : \mathcal{D} \to \mathcal{D}$  in T model the impact of individual instructions i on the domain, and  $\sqcap : \mathcal{D} \times \mathcal{D} \to \mathcal{D}$  is a join operator. Together with a CFG an instance of an (intra-procedural) DFA can be formed, yielding a set of data-flow equations. The join operator ( $\sqcap$ ) and transfer function (T) are instantiated to form IN(i) and OUT(i) functions, which are associated with an instruction i and represent values over  $\mathcal{D}$ . The resulting (recursive) equations are finally solved by iteratively evaluating these functions until a fixed-point is reached [2].

Inter-procedural analyses additionally consider the call relations between functions. In this case, additional data-flow equations are constructed modeling function calls and returns [2]. Often these analyses are context-sensitive, i.e., the analyses distinguish between (bounded) chains of functions calls. Such a chain of nested function calls is then called a call string, which defines a calling context that can be distinguished from other parts of the program calling the same function. Call strings typically have a length limit. The longer the call strings, the higher the ability to distinguish different contexts. Consequently, the analysis results are more precise. Increasing the call string length may also increase the computation complexity and the required memory footprint since additional data-flow equations are created for each context. A call string length of zero corresponds to a context insensitive data-flow analysis.

#### 3. CACHE OCCUPANCY ANALYSES

We present how to compute the cache's occupancy, which ca be used to bound timing, using an inter-procedural data-flow analysis (iDFA) and a tailored stack cache analysis.

#### 3.1 Inter-procedural Data-flow Analysis

The domain of the iDFA approach are positive integer values in  $\mathcal{D} = \{0, \dots, |SC|\}$ , where |SC| represents the stack

cache's size. Since both, the min. and the max. occupancy are needed, two analysis problems have to be defined. We will start with the max. occupancy. The analysis starts at the program entry, where the occupancy is assumed to be 0. It then propagates occupancy values along all execution paths, while considering the effect of the instructions along the path. Only the stack control instructions (see Section 2) can have an impact: (1) sres instructions increase occupancy by their argument k, (2) sens instructions make sure that the occupancy is larger than k, and (3) sfree instructions reduce the occupancy by k. The resulting data-flow equation for an instruction i are given below: